About Mess Framework

Mess provides tools for memory-system benchmarking, simulation, and profiling to support research in HPC and AI systems.

The Story of Mess

From fragmented tools to a unified framework—the journey of bandwidth-latency curves

The Problem

Finding Common Ground

Memory system benchmarking, simulation, and application profiling existed as separate, decoupled tools. The question arose: could we find a common foundation that unifies these approaches?

Is there any common ground?

The Insight

Bandwidth-Latency Curves

Memory system performance isn't just about latency or bandwidth alone. We proposed bandwidth-latency curves as a unified observation that captures the full performance spectrum of memory systems.

A new way to understand memory performance

The Benchmark

Mess Benchmark Born

These curves became the foundation of Mess Benchmark—a comprehensive characterization tool generating curves for each ratio, showcasing sustained bandwidth, peak performance, and latency across all operational points.

If STREAM reports maximum sustained bandwidth, why do we measure 50% more?

The difference: Reported (application level) vs. Measured (HW counters) due to write-allocate policy

The Gap

Simulator Reality Check

When we generated the same curves for popular simulators, they differed significantly from actual hardware measurements. This raised critical questions about simulator accuracy and usability.

Why such a large performance gap?

Open Questions:

- Row buffer statistics accuracy

- CPU-Memory simulator interface

- Simulator design vs. user setup errors

- Where is the user manual?

The Solution

Bridging Hardware and Simulation

We developed a method to plug measured curves directly into simulators, enabling them to accurately model target systems without complex low-level configuration.

Fast, accurate simulation with real hardware profiles

Application Profiling

Positioning Real Workloads

With measured curves from the benchmark, we can now position applications in the bandwidth-latency space, correlating memory behavior with runtime activities and source code.

Understanding where your application lives in the BW-latency space

The Common Ground

Mission Accomplished

By unifying benchmarking, simulation, and profiling through bandwidth-latency curves, Mess provides the common ground we sought—a single framework that serves researchers, developers, and architects.

One framework, three perspectives, infinite insights

Impact & Adoption

Growing Ecosystem

Mess is now integrated with BSC performance analysis tools and prediction models like PROFET. The framework supports all major ISAs (x86, ARM, Power, RISC-V, PTX) and memory technologies (DDR4/5, HBM2/2E, Optane, CXL).

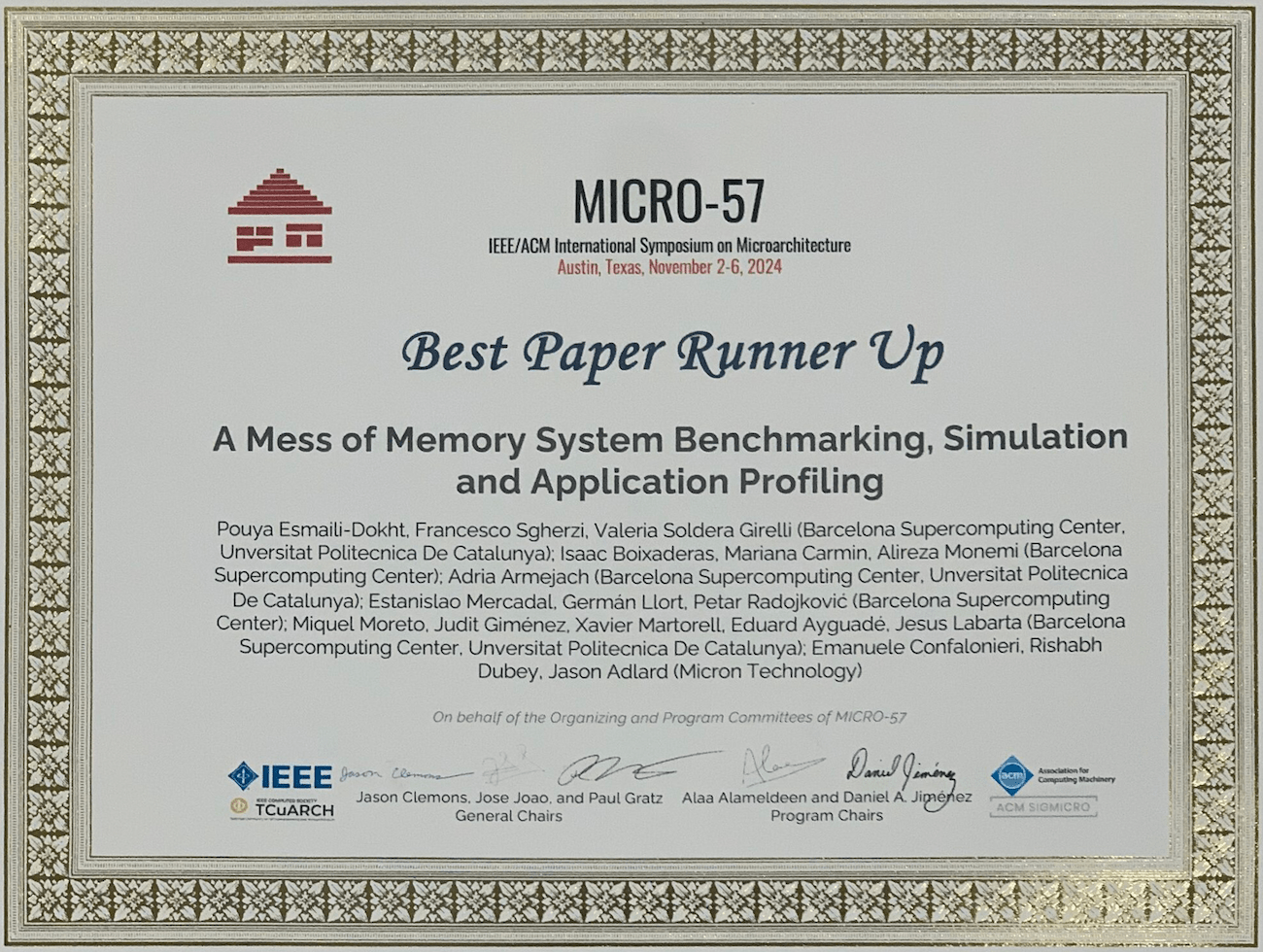

Recognized as MICRO-57 Best Paper Runner-Up

Award Recognition

MICRO-57 Best Paper Runner-Up

Our research on memory system analysis and benchmarking was recognized as Best Paper Runner-Up at the 57th IEEE/ACM International Symposium on Microarchitecture (MICRO-57). This work forms the foundation of the tutorials and resources we share with the research community.

Key Contributors

Meet the main author and team leader driving Mess Framework development

Pouya Esmaili-Dokht

Lead Developer, Mess Framework

Barcelona Supercomputing Center

Pouya Esmaili-Dokht is the leading developer of Mess framework and a third year PhD student at the Universitat Politecnica de Catalunya (UPC), Spain. He earned his MSc degree in computer architecture at UPC in 2019. He is currently a Research Engineer in the memory systems team of Barcelona Supercomputing Center (BSC). He is collaborating with Micron Technology, Inc., on emerging near/in-memory architectures, memory system performance characterization and simulation.

Petar Radojkovic

Memory Systems Group Leader

Barcelona Supercomputing Center

Petar Radojkovic is founder of the BSC Memory system team which he has been leading since 2014. During his management he collaborated with industry partners such as Samsung, and Micron technology. He received his MSc degree in electrical engineering and computer science from the University of Belgrade (Serbia) in 2006. He continued his studies in UPC where he got his MSc and PhD in computer architecture in 2009 and 2013. Petar has been with the BSC since 2006.

Part of BSC Memory Systems Team

Mess Framework is developed by the Memory Systems team at the Barcelona Supercomputing Center (BSC).

Our team focuses on designing and evaluating next-generation memory architectures for high-performance computing and artificial intelligence. We address critical challenges in memory system performance, power efficiency, and reliability.

For over a decade, we have collaborated with industry leaders like Samsung and Micron Technology, developing innovative solutions for memory system benchmarking, simulation, application profiling, and processing-in-memory technologies.

Get in Touch

Have questions or want to collaborate? We'd love to hear from you.

Location

Barcelona Supercomputing Center (BSC)

Plaça Eusebi Güell, 1-3

08034 Barcelona, Spain

For academic collaborations and research partnerships, please reach out to Petar Radojkovic